|

Circuits designed by David Johnson,

P.E.

Last Updated on:

Saturday, December 23, 2017 03:21 PM

Master Category List - Dave's Circuits

The contents &

graphics of Discovercircuits.com are copyright protected.

LINKING to Dave's circuits is permitted but DO NOT COPY any files to your WEB

SITE server |

|

|

|

|

|

|

|

More

Driver Circuits

Relay Circuits

PWM

|

|

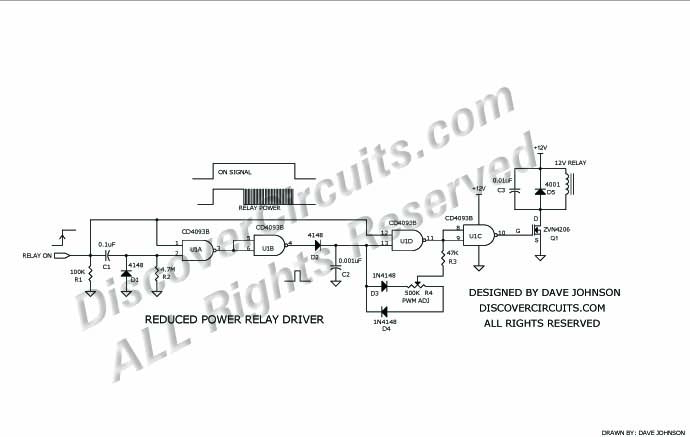

Reduced

Power Relay Driver

Aug 3, 2008 |

Relays can handle a lot of power. However, for certain power sensitive

designs you would like to reduce the power needed to hold a relay closed.

The circuit below performs such a task. It uses a single CD4093 quad NAND

gate. When the “on” logic input signal is detected, the relay is first

pulsed on for about 500ms. This is sufficient time to insure the relay is

fully closed. After that initial pulse the relay is then driven with a

square wave signal, whose duty cycle can be adjusted. The signal duty cycle

can be adjusted from about 10% to 90%. In most cases a 50% duty cycle will

hold the relay closed. This reduces the average DC current required by the

same factor, which means a 4:1 reduction in power. The circuit can operate over a

wide 3v to 15v range. |

|

|

|

Click on Drawing Below to view PDF version of Schematic |

|

|

|

|

|